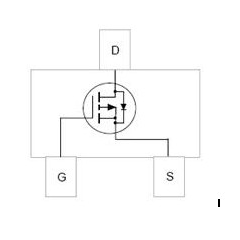

Primum MOSFET genus et structura, MOSFET est FET (alia est JFET), confici in genus auctum vel deperditionem, P-alveum vel N-canale quattuor generum, sed ipsa applicatio N tantum aucta. -canale MOSFETs et auctus P-alvei MOSFETs, ita fere ad NMOSFET, seu PMOSFET referendum est, ut vulgo NMOSFET nominantur, vel PMOSFET ad haec duo referuntur. genera earum. Ad haec duo genera MOSFETs, NMOSFETs auctae communius adhibentur ob repugnantiam et facilitatem fabricandi. Ergo NMOSFETs plerumque adhibentur in mutandi copia et motoriis applicationibus coegi, et sequens introductio etiam in NMOSFETs tendit. capacitas parasitica inter tres fibulas ecclesiae existitMOSFETquae non indiget, sed ex processu vestibulorum limitibus. Praesentia capacitatis parasiticae eam facit aliquantulum insidiose ad excogitandum vel in circuitu aurigae eligendum. Est diode parasitica inter secessum et fontem. Hoc corpus diode dicitur et in oneribus inductoriis ut motoribus magni momenti est. Obiter corpus diode in singulis MOSFETs tantum adest et plerumque intus in chip IC non adest.

Nunc theMOSFETapplicationes low-voltages repellere, cum usus 5V copiae virtutis, hoc tempore si structuram polorum totem traditionalem uteris, propter transitum erit gutta circa 0.7V voltage, unde in actu finali ad portam in intentione solum est. 4.3 V. Hoc tempore, portae nominalis 4.5V MOSFET intentione de quibusdam periculis existentibus eligimus. Idem problema occurrit in usu 3V vel aliis occasionibus facultatis humili intentione supplendi. Dual voltage in quibusdam circuitibus moderandis adhibetur, ubi sectione logica typica utitur 5V vel 3.3V voltage digitalis et in sectione potentia utitur 12V vel etiam superiore. Duae voltages connexae sunt utens communi loco. Hoc postulat utendi ambitus qui latus humilem intentione permittit ut MOSFET in alta intentione latus efficaciter moderaretur, dum MOSFET in alta parte intentionis easdem difficultates subibit, de quibus in 1 et 2;

In omnibus tribus casibus, totius poli compages in output requisitis occurrere non potest, et multi off-Plute MOSFET agitator ICs non videntur portae intentione limitem structuram includere. Initus intentionis valorem certum non est, cum tempore vel aliis factoribus variatur. Haec varietas facit intentionem activitatis quae MOSFET per PWM ambitum instabilem facit. Ut MOSFET tuta ab alta porta voltages, multi MOSFETs in intentione regulatores aedificaverunt ut amplitudinem portae intentionis fortiter circumscriberent. In hoc casu, cum voltage coegi plus quam ordinator voltage, magnam vim static simul efficiet, si simpliciter uteris principium resistor voltage divisoris ad reducendum portam intentionis, erit relativum excelsum. input voltage, theMOSFETbene operatur, dum inputatio intentionis minuitur cum porta intentione non sufficit ad causam minus quam perficiendam conductionem, inde potentia consummatio crescens.

Circuitus communis relativo hic tantum pro NMOSFET auriga circuii ad analysin simplicem faciendam: Vl et Vh sunt humilis finis et summus finis potentiae copiae, duae voltages idem esse possunt, Vl autem Vh non excedunt. Q1 et Q2 totem polum inverso formant, solitarium ad cognoscendum adhibitum, et simul curandum ut duo tubi agitatoris Q3 et Q4 non eodem tempore conductionis fiant. R2 et R3 praebent intentionem PWM R2 et R3 praebent intentionem PWM intentioni, mutando relationem, permittere potes opus circuii in PWM signo waveformi quod est positio arduus et directus respective. Q3 et Q4 adhibentur ad currentem pulsum, ex tempore, Q3 et Q4 relativo cum Vh et GND, minimum sunt guttae intentionis Vce, haec voltatio gutta fere tantum 0.3V vel multo inferiora est. quam 0.7V Vce R5 et R6 sunt opiniones resistentium, pro porta R5 et R6 sunt opiniones resistentium ad exemplum portae intentionis, quae tunc per Q5 transivit ad generandum opiniones negativas validas in basi Q1 et Q2, ita limitando portae intentione ad valorem finitum. Hic valor R5 et R6 adaptari potest. Denique R1 limitationem basis currentis ad Q3 et Q4 praebet, et R4 limitationem portae currentis ad MOSFETs praebet, quae est limitatio Ice Q3Q4. Acceleratio capacitor supra R4, si opus sit, parallelismo coniungi potest.