MOSFET una ex elementis fundamentalibus in industria semiconductoris. In circulis electronicis, MOSFET plerumque in circuitibus amplificantibus potentiae vel mutandi copiae circuitus potentiae adhibetur et late adhibetur. Infra,OLUKEYexplicatio tibi explicatio principii MOSFET operationis dabit et structuram internam MOSFET analysi.

Quid est?MOSFET

MOSFET, Oxide Metallum Semiconductor Transistor (MOSFET). Est ager effectus transistoris qui late in circulis analogorum et in circulis digitalibus potest adhiberi. Secundum verticitatem differentiam sui "canali" (portarii operantis), in duo genera dividi potest: "N-type" et "P-type", quae saepe NMOS et PMOS vocantur.

MOSFET opus principium

MOSFET dividi potest in amplificationem generis et deperditionem generis secundum modum operantem. Amplificatio generis ad MOSFET cum nulla intentione applicatur et nulla conductivum alveum. Deperditio generis ad MOSFET refertur, ubi nulla intentionis inclinatio applicatur. Prolixa alveus apparebit.

In applicationibus actualibus, sunt tantum generis amplificationis N-canni et amplificationis P-alvei MOSFETs generis. Cum NMOSFETs parvam in statu resistentiam habent et faciles fabricare, NMOS communior est quam PMOS in applicationibus actualibus.

Modus amplificationis MOSFET

Coniunctiones PN retro ad dorsum duae sunt inter exhaurire D et fontem S amplificationis modi MOSFET. Cum portae-fontis intentione VGS=0, etiam si fons exhauriens intentionis VDS addatur, semper PN coniunctio est in statu reverso, nec est alveus conductivus inter exhaurire et fontem (nulla vena defluit. ). Ideo vena ID=0 hoc tempore exhauriebatur.

Hoc tempore, si deinceps intentio inter portam et fontem accedit. Hoc est, VGS>0, tunc campus electricus cum porta varius cum P-typo pii substrato generabitur in strato insulato SiO2 inter portam electrode et silicon distent. Quia iacuit oxydatum insulare, intentione VGS ad portam applicata currentem producere non potest. Genitur capacitor ex utraque parte strati oxydi, et VGS ambitus aequivalens hunc capacitorem accusat. Et generale campum electricum, ut VGS lente surgit, a positivo portae intentione attractum. Magnus numerus electronicorum ex altera parte capacitoris huius (capacitoris) cumulant et canalem n-typum conductivum e fonte exhauriunt. Cum VGS in intentione VT tubi (vulgo 2V fere) superat, tubus canalis N mox agere incipit, venam exhaurire generans ID. Portam-fontem intentionem vocamus cum alveus primum incipit generare tractum in intentione. Vulgo exprimitur VT.

Moles portae voltage VGS moderante vim vel debilitatem campi electrica mutat, et effectus moderandi magnitudinem exhauriendi id fieri potest. Hoc etiam magni momenti notum est MOSFETs qui electricis agris utuntur ad refrenandum currentem, unde etiam ager effectus transistores appellatur.

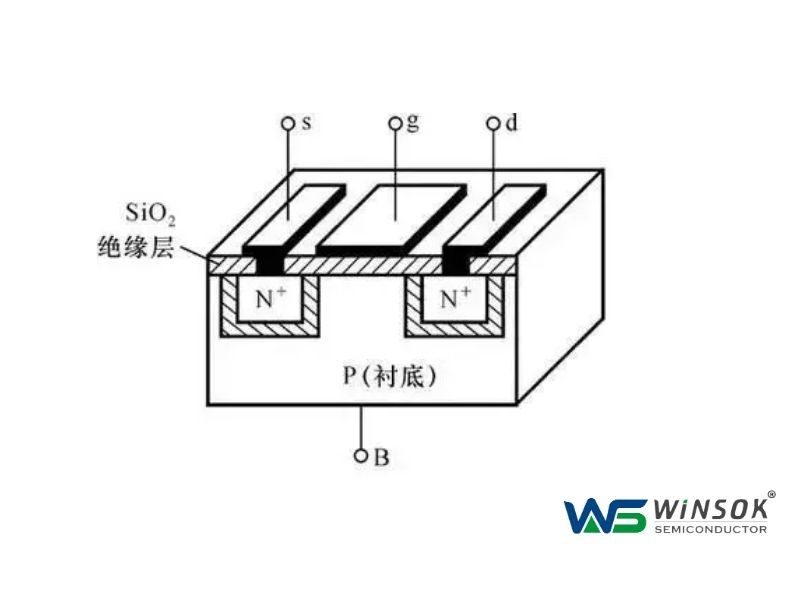

MOSFET internum compages

In P-typo Pii substrato cum humili attentione impuritatis, duae regiones N+ cum magna intentione immunditiae fiunt, et duae electrodes e metallo educuntur ad aluminium ad exhauriendum d et principium respective. Tum superficies semiconductor tegitur dioxide silicone (SiO2) strato insulante, et aluminium electrode in strato insulante inter exhaurire et fontem cui portae g inservire instituitur. Electrode B etiam in subiecto educitur, cum N canali modum MOSFET amplificationem efformans. Idem valet de formatione interna P-channel-type MOSFETs amplificationis.

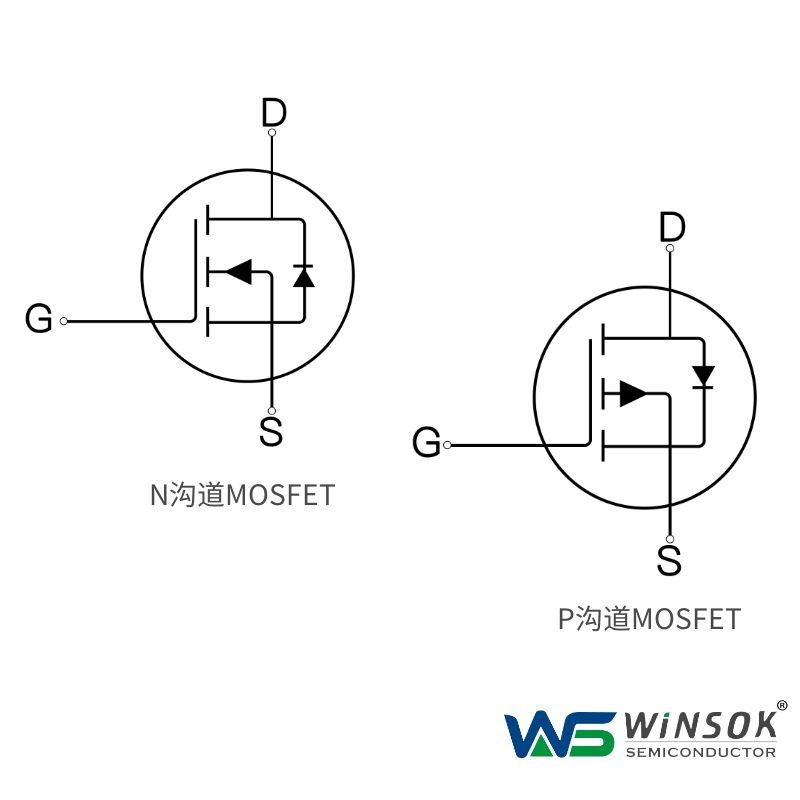

N-canalis MOSFET et P-fluvii MOSFET ambitus symbolorum

Pictura supra figuram MOSFET ambitum ostendit. In tabula D exhaurit, S fons est, G porta est, et sagitta in medio subjectum repraesentat. Si sagitta interna demonstrat, N-canalem MOSFET indicat, et si sagitta exteriora demonstrat, P-canalem MOSFET indicat.

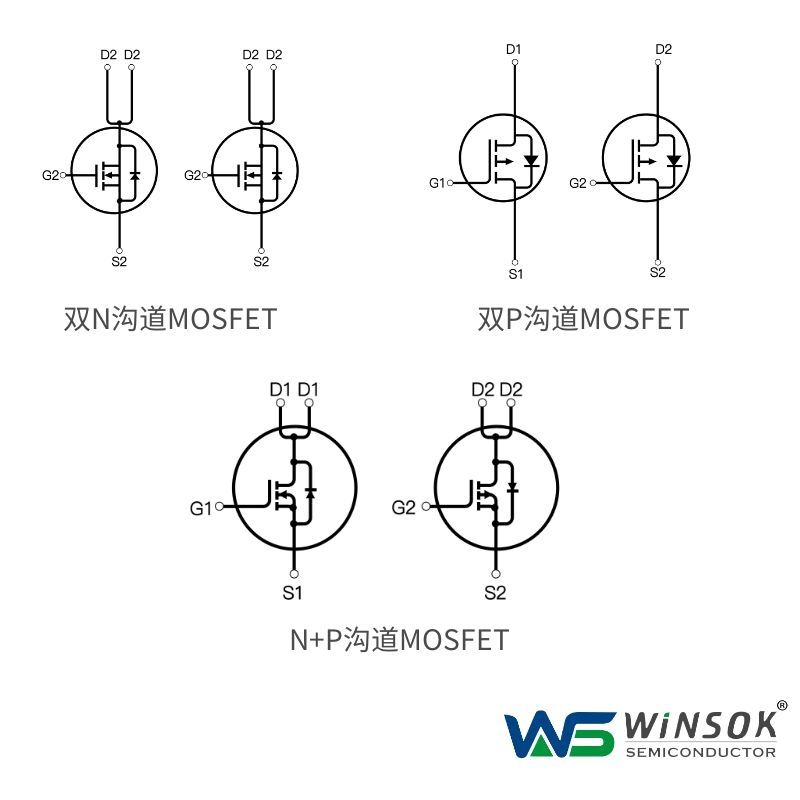

Dual N-canalis MOSFET, dualis P alvei MOSFET et N+P-alvei MOSFET ambitus symbolorum.

Revera, durante processu fabricandi MOSFET, substratum cum fonte iungitur antequam officinas relinquat. Ideo in regula symboli, sagitta symboli subiectum repraesentans debet etiam coniungi cum fonte ad hauriendum et fontem distinguendum. Verticitas voltagenae a MOSFET usui tradito transistori similis est. N-alveum NPN transistori simile est. Exhaurire D cum electro positivi coniungitur et principium S cum electrode negativo coniungitur. Cum porta G positivum intentionem habet, canalis conductivus formatur et N-canali MOSFET laborare incipit. Similiter canale PNP transistori simile est. Detritum D cum electrode negativo coniungitur, fons S cum electrode positivo coniungitur, et cum porta G negativam intentionem habet, canalis conductivus formatur et P-alvei MOSFET laborare incipit.

MOSFET commutatione damnum principium

Utrum NMOS vel PMOS sit, conductio interna resistentia genita postquam in versa est, ut hodierna resistentia internam industriam consumat. Haec pars industriae consumptio consummatio conductio appellatur. Eligentes MOSFET cum parva conductione resistentia interna, consummationem conductionem efficaciter reducere poterit. Hodierna resistentia interna humilis-potestatis MOSFETs fere circiter decem milliohmorum est, et etiam plures decies centena milia sunt.

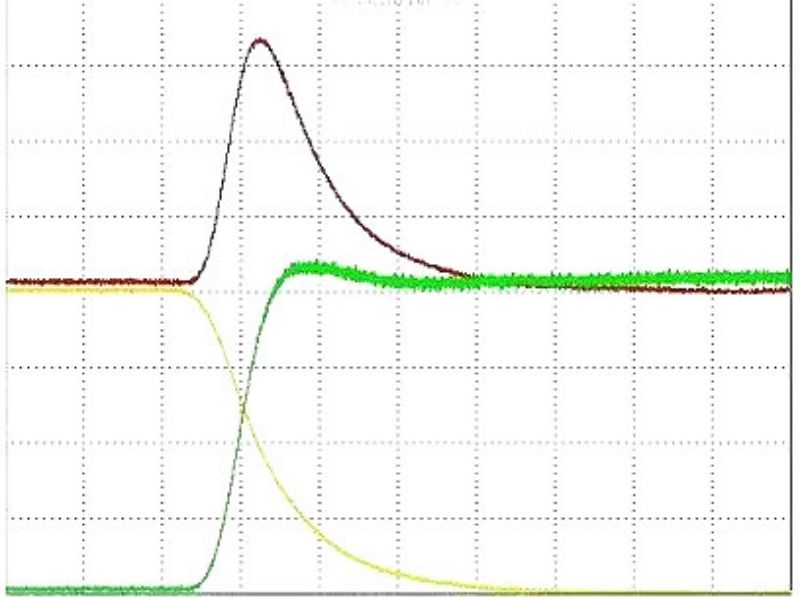

Quando MOS vertitur in et terminatur, non debet fieri in instanti. Voltatio in utraque MOS decrementum efficax erit, et currens per eam incrementum habebit. Temporis, amissio MOSFET producto voltatione et praesenti, quod est damnum mutativum. In universum, damna mutandi multo maiora sunt quam damna conductionis et celerius mutandi frequentia, quo maiora sunt damna.

Productum voltage et currens tempore conductionis amplissimum est, ex maximis dispendiis proveniens. Damna permutatio duobus modis minui potest. Unum est minuere tempus commutationis, quod efficaciter potest minuere damnum in singulis vicis; altera est ad commutationes frequentiae reducendas, quae numerum virgarum per unitatem temporis minuere possunt.

Haec accurata explicatio est principii schematis MOSFET operantis et analysis structurae internae MOSFET. Ut plura de MOSFET discas, salve ut consulas OLUKEY ut tibi cum MOSFET technicis subsidium praebeat!